# hdlConvertor

[](https://circleci.com/gh/Nic30/hdlConvertor)

[](https://ci.appveyor.com/project/nic30/hdlconvertor)

[](http://badge.fury.io/py/hdlConvertor)

[](https://img.shields.io/pypi/pyversions/hdlConvertor.svg)

[](https://gitter.im/hdlConvertor/community?utm_source=badge&utm_medium=badge&utm_campaign=pr-badge)

[](https://coveralls.io/github/Nic30/hdlConvertor?branch=master)(generated code)

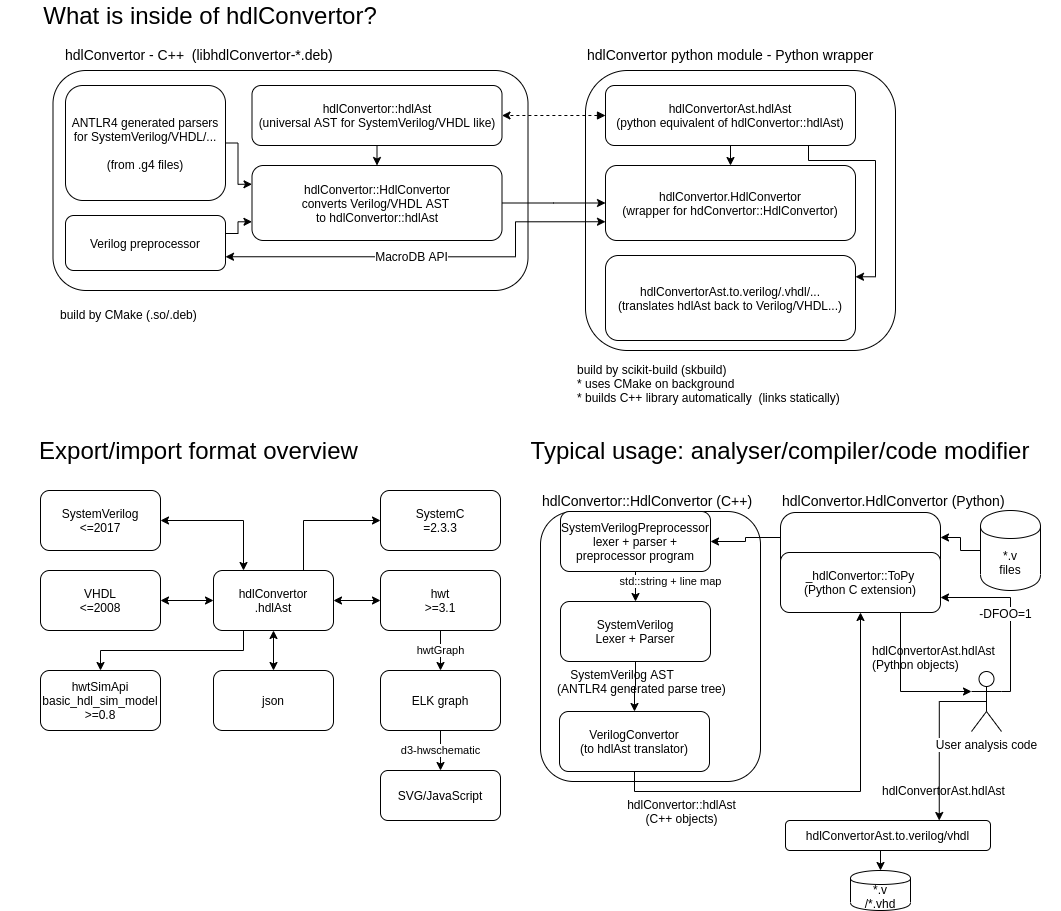

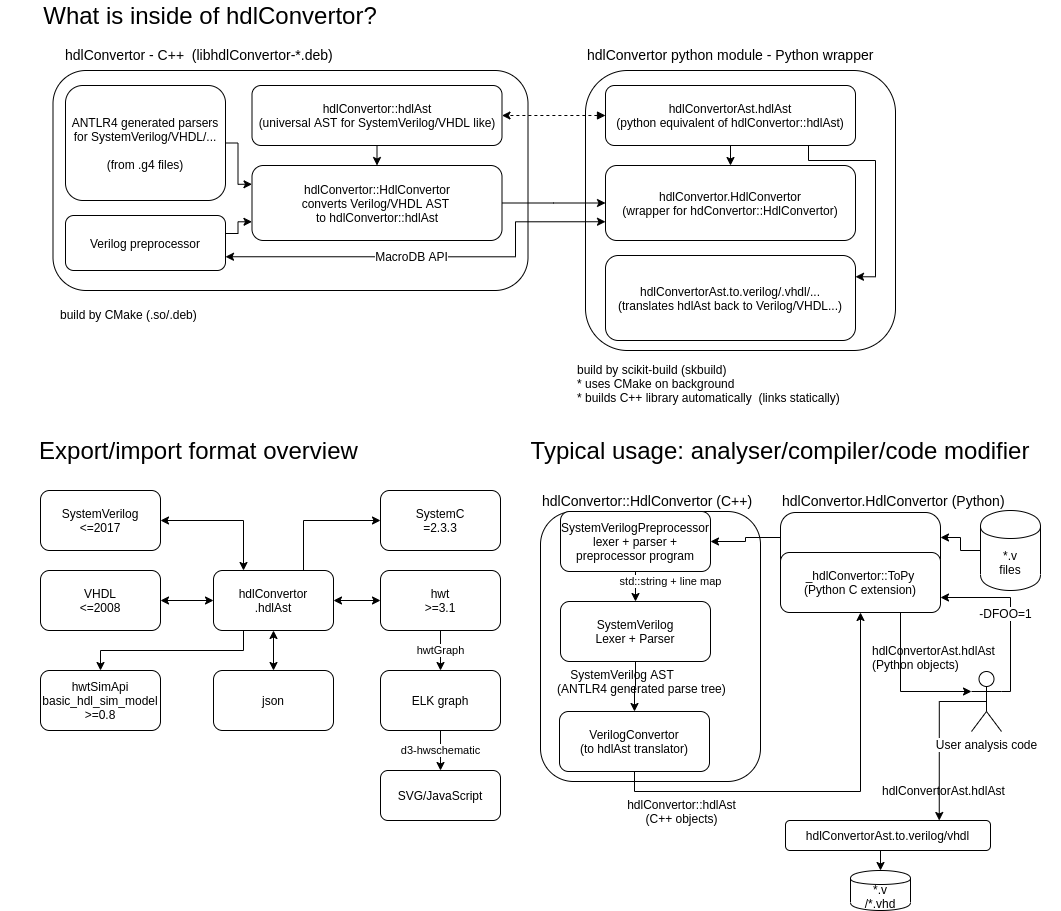

This library is a System Verilog and VHDL parser, preprocessor and code generator for Python/C++.

It contains:

* ANTLR4 generated VHDL/(System) Verilog parser with full language support.

* Convertors from raw VHDL/SV AST to universal HDL AST ([hdlConvertor::hdlAst](https://github.com/Nic30/hdlConvertor/tree/master/include/hdlConvertor/hdlAst) and it's [python equivalent](https://github.com/Nic30/hdlConvertorAst/tree/master/hdlConvertorAst/hdlAst).).

* Convertors from this HDL AST [to SV/VHDL/JSON](https://github.com/Nic30/hdlConvertorAst/tree/master/hdlConvertorAst/to) and other formats.

* Compiler focused [utils](https://github.com/Nic30/hdlConvertorAst/tree/master/hdlConvertorAst/translate) for manipulation with HDL AST.

* HdlAstVisitor, id resolution, sensitivity detection, vhdl <-> verilog type conversion, ...

### Supported languages:

* [IEEE 1076-2008 (VHDL 2008)](https://ieeexplore.ieee.org/document/4772740) and all previous standard, (currently without `tool_directive` and `PSL`)

* [IEEE 1076-2019] WIP

* [IEEE 1800-2017 (SystemVerilog 2017)](https://ieeexplore.ieee.org/document/8299595) and all previous standards.

## Installation

Linux:

Installing dependencies (Ubuntu 20.10)

```

# we recommend to use gcc>=9, Visual Studio 2017 or equivalent

sudo apt install build-essential uuid-dev cmake default-jre python3 python3-dev python3-pip libantlr4-runtime-dev antlr4 ninja-build

```

Installing this library

```

# note this may be older version than you see in repo

sudo pip3 install hdlConvertor

# or download repository and run

sudo pip3 install --upgrade --force-reinstall --no-cache-dir git+https://github.com/Nic30/hdlConvertorAst.git

sudo pip3 install -r requirements.txt

sudo python3 setup.py install

# if you are using version from git rather uninstall

# old library first if required

# sudo pip3 uninstall hdlConvertor

```

Installer also supports other options which may be usefull

```

python setup.py install --prefix /tmp/python_install/ --build-type Debug -- -DANTLR_JAR_LOCATION=/antlr-4.7.1-complete.jar -- VERBOSE=1

```

You can also install only C++ library/generate .deb package (nothing specific, just normal cmake-based library)

```

mkdir build && cd build

cmake .. && cmake . --build

cpack # to generate .deb package

```

Windows:

Take a look at appveyor.yml and [doc/windows_installation_and_build.rst](doc/windows_installation_and_build.rst). It is required to download antlr4 first and have visual studio or other c++ compiler installed.

## Usage

The HDL AST (the parsed code) is represented by objects from `hdlConvertor.hdlAst`. Parsing and code modification is straightforward, as you can see in following example [](https://mybinder.org/v2/gh/Nic30/hdlConvertor/master?filepath=notebooks%2F01_parse_and_dump.ipynb)

### Similar projects:

(Tell us If you know about some other project!)

* [circt](https://github.com/llvm/circt) - C++, LLVM based infrastructutre for SV/VHDL/FIRRTL compilation and simulation

* [cl-vhdl](https://github.com/mabragor/cl-vhdl) - lisp, Parser of VHDL into lisp-expressions

* [HDL_ANTLR4](https://github.com/denisgav/HDL_ANTLR4) - C# projects that use ANTLR4 library to analyse VHDL and Verilog code

* [hdlparse](https://github.com/kevinpt/hdlparse/) - vhdl/verilog parser in python

* [ieee1800_2017](https://github.com/veriktig/ieee1800_2017) - Java, SystemVerilog preprocessor

* [istyle-verilog-formatter](https://github.com/thomasrussellmurphy/istyle-verilog-formatter) - c++, Verilog formatter

* [Pyverilog](https://github.com/PyHDI/Pyverilog) - python verilog toolkit

* [pyvsc](https://github.com/fvutils/pyvsc) - C++, library for Verification Stimulus and Coverage description

* [pyVHDLParser](https://github.com/Paebbels/pyVHDLParser) - python vhdl parser with 2008 support

* [RgGen](https://github.com/rggen/rggen) - CSR (Configuration and Status Registers) generator

* [rust_hdl](https://github.com/kraigher/rust_hdl) - rust vhdl 2008 parser

* [slang](https://github.com/MikePopoloski/slang) - Parser and compiler library for SystemVerilog.

* [sv-parser](https://github.com/dalance/sv-parser) - Rust, SystemVerilog parser library fully complient with IEEE 1800-2017

* [systemc-clang](https://github.com/anikau31/systemc-clang) - SystemC Parser using the Clang Front-end

* [v2sc](https://github.com/denisgav/v2sc) - vhdl to systemc

* [veelox](https://github.com/martinda/veelox) - Java+ANTLR, An experiment in SystemVerilog Preprocessing

* [verible](https://github.com/chiplicity/verible) -C++, SystemVerilog parser, style-linter, and formatter

* [verilog-parser](https://github.com/ben-marshall/verilog-parser) - A Flex/Bison Parser for the IEEE 1364-2001 Verilog Standard.

* [vbpp](https://github.com/balanx/vbpp) - C, Verilog PreProcessor

* [tree-sitter-verilog](https://github.com/tree-sitter/tree-sitter-verilog) - JS, Verilog grammar for tree-sitter

* [Verilog-Perl](https://metacpan.org/pod/Verilog-Perl)

* [vpp.pl](https://www.beyond-circuits.com/wordpress/vpp-pl-man-page/) - verilog preprocessor with integrated Perl

* [sv2v](https://github.com/zachjs/sv2v)- Haskell, SystemVerilog to Verilog

* [Surelog](https://github.com/alainmarcel/Surelog) - C++, System Verilog 2017 Pre-processor and parser

* [verible](https://github.com/google/verible) - C++, System Verilog 2017 parser

* [UHDM](https://github.com/alainmarcel/UHDM) - rust, universal hardware data model

Raw data

{

"_id": null,

"home_page": "https://github.com/Nic30/hdlConvertor",

"name": "hdlConvertor-binary",

"maintainer": "",

"docs_url": null,

"requires_python": "",

"maintainer_email": "",

"keywords": "hdl,vhdl,verilog,system verilog,parser,preprocessor,antlr4",

"author": "Michal Orsak",

"author_email": "Nic30original@gmail.com",

"download_url": "https://files.pythonhosted.org/packages/c9/8c/9623469a89adda7772e456ce6b0d8c52ecc381e5e05408925b54e0619ad4/hdlConvertor-binary-2.3.tar.gz",

"platform": null,

"description": "# hdlConvertor\n[](https://circleci.com/gh/Nic30/hdlConvertor)\n[](https://ci.appveyor.com/project/nic30/hdlconvertor)\n[](http://badge.fury.io/py/hdlConvertor)\n[](https://img.shields.io/pypi/pyversions/hdlConvertor.svg)\n[](https://gitter.im/hdlConvertor/community?utm_source=badge&utm_medium=badge&utm_campaign=pr-badge)\n[](https://coveralls.io/github/Nic30/hdlConvertor?branch=master)(generated code)\n\nThis library is a System Verilog and VHDL parser, preprocessor and code generator for Python/C++.\nIt contains:\n\n * ANTLR4 generated VHDL/(System) Verilog parser with full language support.\n * Convertors from raw VHDL/SV AST to universal HDL AST ([hdlConvertor::hdlAst](https://github.com/Nic30/hdlConvertor/tree/master/include/hdlConvertor/hdlAst) and it's [python equivalent](https://github.com/Nic30/hdlConvertorAst/tree/master/hdlConvertorAst/hdlAst).).\n * Convertors from this HDL AST [to SV/VHDL/JSON](https://github.com/Nic30/hdlConvertorAst/tree/master/hdlConvertorAst/to) and other formats.\n * Compiler focused [utils](https://github.com/Nic30/hdlConvertorAst/tree/master/hdlConvertorAst/translate) for manipulation with HDL AST.\n * HdlAstVisitor, id resolution, sensitivity detection, vhdl <-> verilog type conversion, ...\n\n\n\n\n### Supported languages:\n* [IEEE 1076-2008 (VHDL 2008)](https://ieeexplore.ieee.org/document/4772740) and all previous standard, (currently without `tool_directive` and `PSL`)\n* [IEEE 1076-2019] WIP\n* [IEEE 1800-2017 (SystemVerilog 2017)](https://ieeexplore.ieee.org/document/8299595) and all previous standards.\n\n\n## Installation\n\nLinux:\nInstalling dependencies (Ubuntu 20.10)\n```\n# we recommend to use gcc>=9, Visual Studio 2017 or equivalent\nsudo apt install build-essential uuid-dev cmake default-jre python3 python3-dev python3-pip libantlr4-runtime-dev antlr4 ninja-build\n```\n\nInstalling this library\n```\n# note this may be older version than you see in repo\nsudo pip3 install hdlConvertor\n\n# or download repository and run\nsudo pip3 install --upgrade --force-reinstall --no-cache-dir git+https://github.com/Nic30/hdlConvertorAst.git\nsudo pip3 install -r requirements.txt\nsudo python3 setup.py install\n\n# if you are using version from git rather uninstall\n# old library first if required\n# sudo pip3 uninstall hdlConvertor\n```\n\nInstaller also supports other options which may be usefull\n```\npython setup.py install --prefix /tmp/python_install/ --build-type Debug -- -DANTLR_JAR_LOCATION=/antlr-4.7.1-complete.jar -- VERBOSE=1\n```\n\nYou can also install only C++ library/generate .deb package (nothing specific, just normal cmake-based library)\n```\nmkdir build && cd build\ncmake .. && cmake . --build\ncpack # to generate .deb package\n```\n\nWindows:\n\nTake a look at appveyor.yml and [doc/windows_installation_and_build.rst](doc/windows_installation_and_build.rst). It is required to download antlr4 first and have visual studio or other c++ compiler installed.\n\n\n## Usage\n\nThe HDL AST (the parsed code) is represented by objects from `hdlConvertor.hdlAst`. Parsing and code modification is straightforward, as you can see in following example [](https://mybinder.org/v2/gh/Nic30/hdlConvertor/master?filepath=notebooks%2F01_parse_and_dump.ipynb)\n\n\n\n### Similar projects:\n(Tell us If you know about some other project!)\n\n* [circt](https://github.com/llvm/circt) - C++, LLVM based infrastructutre for SV/VHDL/FIRRTL compilation and simulation\n* [cl-vhdl](https://github.com/mabragor/cl-vhdl) - lisp, Parser of VHDL into lisp-expressions\n* [HDL_ANTLR4](https://github.com/denisgav/HDL_ANTLR4) - C# projects that use ANTLR4 library to analyse VHDL and Verilog code\n* [hdlparse](https://github.com/kevinpt/hdlparse/) - vhdl/verilog parser in python\n* [ieee1800_2017](https://github.com/veriktig/ieee1800_2017) - Java, SystemVerilog preprocessor\n* [istyle-verilog-formatter](https://github.com/thomasrussellmurphy/istyle-verilog-formatter) - c++, Verilog formatter\n* [Pyverilog](https://github.com/PyHDI/Pyverilog) - python verilog toolkit\n* [pyvsc](https://github.com/fvutils/pyvsc) - C++, library for Verification Stimulus and Coverage description\n* [pyVHDLParser](https://github.com/Paebbels/pyVHDLParser) - python vhdl parser with 2008 support\n* [RgGen](https://github.com/rggen/rggen) - CSR (Configuration and Status Registers) generator\n* [rust_hdl](https://github.com/kraigher/rust_hdl) - rust vhdl 2008 parser\n* [slang](https://github.com/MikePopoloski/slang) - Parser and compiler library for SystemVerilog.\n* [sv-parser](https://github.com/dalance/sv-parser) - Rust, SystemVerilog parser library fully complient with IEEE 1800-2017\n* [systemc-clang](https://github.com/anikau31/systemc-clang) - SystemC Parser using the Clang Front-end\n* [v2sc](https://github.com/denisgav/v2sc) - vhdl to systemc\n* [veelox](https://github.com/martinda/veelox) - Java+ANTLR, An experiment in SystemVerilog Preprocessing\n* [verible](https://github.com/chiplicity/verible) -C++, SystemVerilog parser, style-linter, and formatter\n* [verilog-parser](https://github.com/ben-marshall/verilog-parser) - A Flex/Bison Parser for the IEEE 1364-2001 Verilog Standard.\n* [vbpp](https://github.com/balanx/vbpp) - C, Verilog PreProcessor\n* [tree-sitter-verilog](https://github.com/tree-sitter/tree-sitter-verilog) - JS, Verilog grammar for tree-sitter\n* [Verilog-Perl](https://metacpan.org/pod/Verilog-Perl)\n* [vpp.pl](https://www.beyond-circuits.com/wordpress/vpp-pl-man-page/) - verilog preprocessor with integrated Perl\n* [sv2v](https://github.com/zachjs/sv2v)- Haskell, SystemVerilog to Verilog\n* [Surelog](https://github.com/alainmarcel/Surelog) - C++, System Verilog 2017 Pre-processor and parser\n* [verible](https://github.com/google/verible) - C++, System Verilog 2017 parser\n* [UHDM](https://github.com/alainmarcel/UHDM) - rust, universal hardware data model\n\n\n",

"bugtrack_url": null,

"license": "MIT",

"summary": "VHDL and System Verilog parser written in c++",

"version": "2.3",

"project_urls": {

"Homepage": "https://github.com/Nic30/hdlConvertor"

},

"split_keywords": [

"hdl",

"vhdl",

"verilog",

"system verilog",

"parser",

"preprocessor",

"antlr4"

],

"urls": [

{

"comment_text": "",

"digests": {

"blake2b_256": "8ae26fcf1448053405ada691933ed814a8b8a151ee9badcf9fa7f6cad78188de",

"md5": "49e631afc33c6b9c90f3b14cb0edbdd6",

"sha256": "d3c66d2f26bde2a6d92bc209c7e42b16168fc25493c86d61d58f050691845def"

},

"downloads": -1,

"filename": "hdlConvertor_binary-2.3-cp310-cp310-manylinux_2_31_x86_64.whl",

"has_sig": false,

"md5_digest": "49e631afc33c6b9c90f3b14cb0edbdd6",

"packagetype": "bdist_wheel",

"python_version": "cp310",

"requires_python": null,

"size": 1873235,

"upload_time": "2024-01-06T00:37:25",

"upload_time_iso_8601": "2024-01-06T00:37:25.532711Z",

"url": "https://files.pythonhosted.org/packages/8a/e2/6fcf1448053405ada691933ed814a8b8a151ee9badcf9fa7f6cad78188de/hdlConvertor_binary-2.3-cp310-cp310-manylinux_2_31_x86_64.whl",

"yanked": false,

"yanked_reason": null

},

{

"comment_text": "",

"digests": {

"blake2b_256": "63b9e513450a091ddd11a222c0584e6c469e93254c93717494661aba6ed00b9e",

"md5": "e2e1e8aaed7ba9cfaa03115ad5fa3a1f",

"sha256": "e80870720fdc831a44342f8878f0d9d8b991b782ac9ea1020ca074044b0f6a33"

},

"downloads": -1,

"filename": "hdlConvertor_binary-2.3-cp311-cp311-manylinux_2_31_x86_64.whl",

"has_sig": false,

"md5_digest": "e2e1e8aaed7ba9cfaa03115ad5fa3a1f",

"packagetype": "bdist_wheel",

"python_version": "cp311",

"requires_python": null,

"size": 1872274,

"upload_time": "2024-01-06T00:37:28",

"upload_time_iso_8601": "2024-01-06T00:37:28.165073Z",

"url": "https://files.pythonhosted.org/packages/63/b9/e513450a091ddd11a222c0584e6c469e93254c93717494661aba6ed00b9e/hdlConvertor_binary-2.3-cp311-cp311-manylinux_2_31_x86_64.whl",

"yanked": false,

"yanked_reason": null

},

{

"comment_text": "",

"digests": {

"blake2b_256": "34795c68506fb17dda2e471268be50a22d02786b397aa4ec0d0d57c79466ab31",

"md5": "f0eccca3da5eb5d07096f8c2857b7530",

"sha256": "d68d2d2f314c366fe5d47dac55447945a7da3ef9e8873ba1b13dfd107497d9e6"

},

"downloads": -1,

"filename": "hdlConvertor_binary-2.3-cp312-cp312-manylinux_2_31_x86_64.whl",

"has_sig": false,

"md5_digest": "f0eccca3da5eb5d07096f8c2857b7530",

"packagetype": "bdist_wheel",

"python_version": "cp312",

"requires_python": null,

"size": 1867005,

"upload_time": "2024-01-06T00:37:29",

"upload_time_iso_8601": "2024-01-06T00:37:29.885929Z",

"url": "https://files.pythonhosted.org/packages/34/79/5c68506fb17dda2e471268be50a22d02786b397aa4ec0d0d57c79466ab31/hdlConvertor_binary-2.3-cp312-cp312-manylinux_2_31_x86_64.whl",

"yanked": false,

"yanked_reason": null

},

{

"comment_text": "",

"digests": {

"blake2b_256": "a6b039cf0e20384ef8f4bbc19e23badb314166e7dff924a1841d2371b41e6b55",

"md5": "28a41d309a29a33a740905836897b483",

"sha256": "3dd437bc872053ea7d704b86a55623ce7a0bad40e123164962a2bc8929e64363"

},

"downloads": -1,

"filename": "hdlConvertor_binary-2.3-cp38-cp38-manylinux_2_31_x86_64.whl",

"has_sig": false,

"md5_digest": "28a41d309a29a33a740905836897b483",

"packagetype": "bdist_wheel",

"python_version": "cp38",

"requires_python": null,

"size": 1876016,

"upload_time": "2024-01-06T00:37:32",

"upload_time_iso_8601": "2024-01-06T00:37:32.168594Z",

"url": "https://files.pythonhosted.org/packages/a6/b0/39cf0e20384ef8f4bbc19e23badb314166e7dff924a1841d2371b41e6b55/hdlConvertor_binary-2.3-cp38-cp38-manylinux_2_31_x86_64.whl",

"yanked": false,

"yanked_reason": null

},

{

"comment_text": "",

"digests": {

"blake2b_256": "f5fb74390d146b63a73dc50f6ac67d99a38b67d364eb2e00ef9858eca48a1579",

"md5": "a9b968cdddf4fd3ff275160dfa5729ef",

"sha256": "bb3f66aeefe2735d64806e292129a9376399832b968b2f1186a90da61c08cd71"

},

"downloads": -1,

"filename": "hdlConvertor_binary-2.3-cp39-cp39-manylinux_2_31_x86_64.whl",

"has_sig": false,

"md5_digest": "a9b968cdddf4fd3ff275160dfa5729ef",

"packagetype": "bdist_wheel",

"python_version": "cp39",

"requires_python": null,

"size": 1873372,

"upload_time": "2024-01-06T00:37:33",

"upload_time_iso_8601": "2024-01-06T00:37:33.736533Z",

"url": "https://files.pythonhosted.org/packages/f5/fb/74390d146b63a73dc50f6ac67d99a38b67d364eb2e00ef9858eca48a1579/hdlConvertor_binary-2.3-cp39-cp39-manylinux_2_31_x86_64.whl",

"yanked": false,

"yanked_reason": null

},

{

"comment_text": "",

"digests": {

"blake2b_256": "c98c9623469a89adda7772e456ce6b0d8c52ecc381e5e05408925b54e0619ad4",

"md5": "0c21b07ff970adf452148d8a36e74053",

"sha256": "1f6131f76dbf1bc18d5847fe96b8033a5bb14219ebb2eb50b9bec1f3c62df97b"

},

"downloads": -1,

"filename": "hdlConvertor-binary-2.3.tar.gz",

"has_sig": false,

"md5_digest": "0c21b07ff970adf452148d8a36e74053",

"packagetype": "sdist",

"python_version": "source",

"requires_python": null,

"size": 161179,

"upload_time": "2024-01-06T00:37:35",

"upload_time_iso_8601": "2024-01-06T00:37:35.419357Z",

"url": "https://files.pythonhosted.org/packages/c9/8c/9623469a89adda7772e456ce6b0d8c52ecc381e5e05408925b54e0619ad4/hdlConvertor-binary-2.3.tar.gz",

"yanked": false,

"yanked_reason": null

}

],

"upload_time": "2024-01-06 00:37:35",

"github": true,

"gitlab": false,

"bitbucket": false,

"codeberg": false,

"github_user": "Nic30",

"github_project": "hdlConvertor",

"travis_ci": false,

"coveralls": false,

"github_actions": false,

"appveyor": true,

"circle": true,

"requirements": [],

"lcname": "hdlconvertor-binary"

}